PDF) Design And Implementation Of An Enhanced Dds Based Digital Modulator For Multiple Modulation Schemes

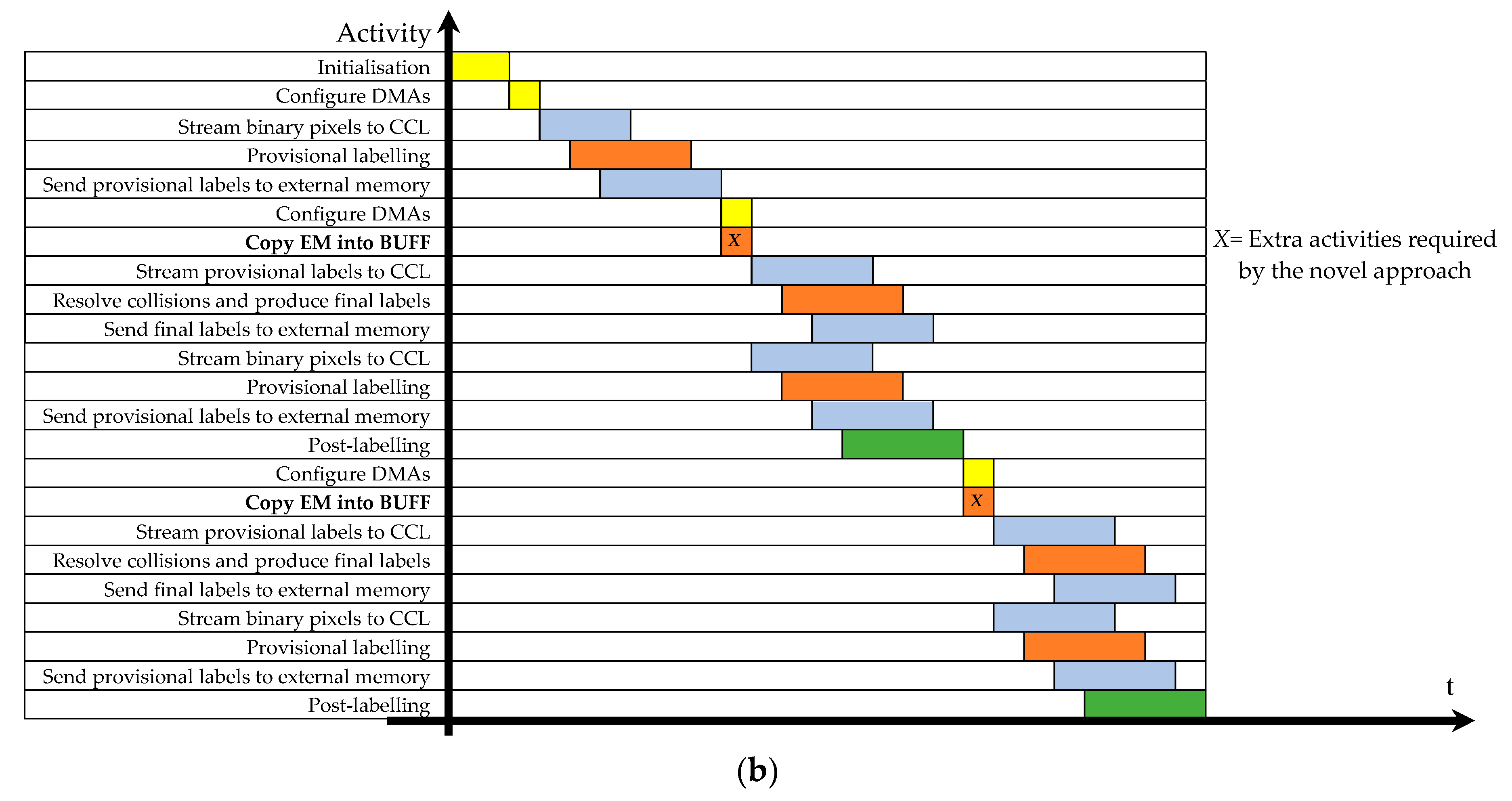

Electronics | Free Full-Text | A Parallel Connected Component Labeling Architecture for Heterogeneous Systems-on-Chip

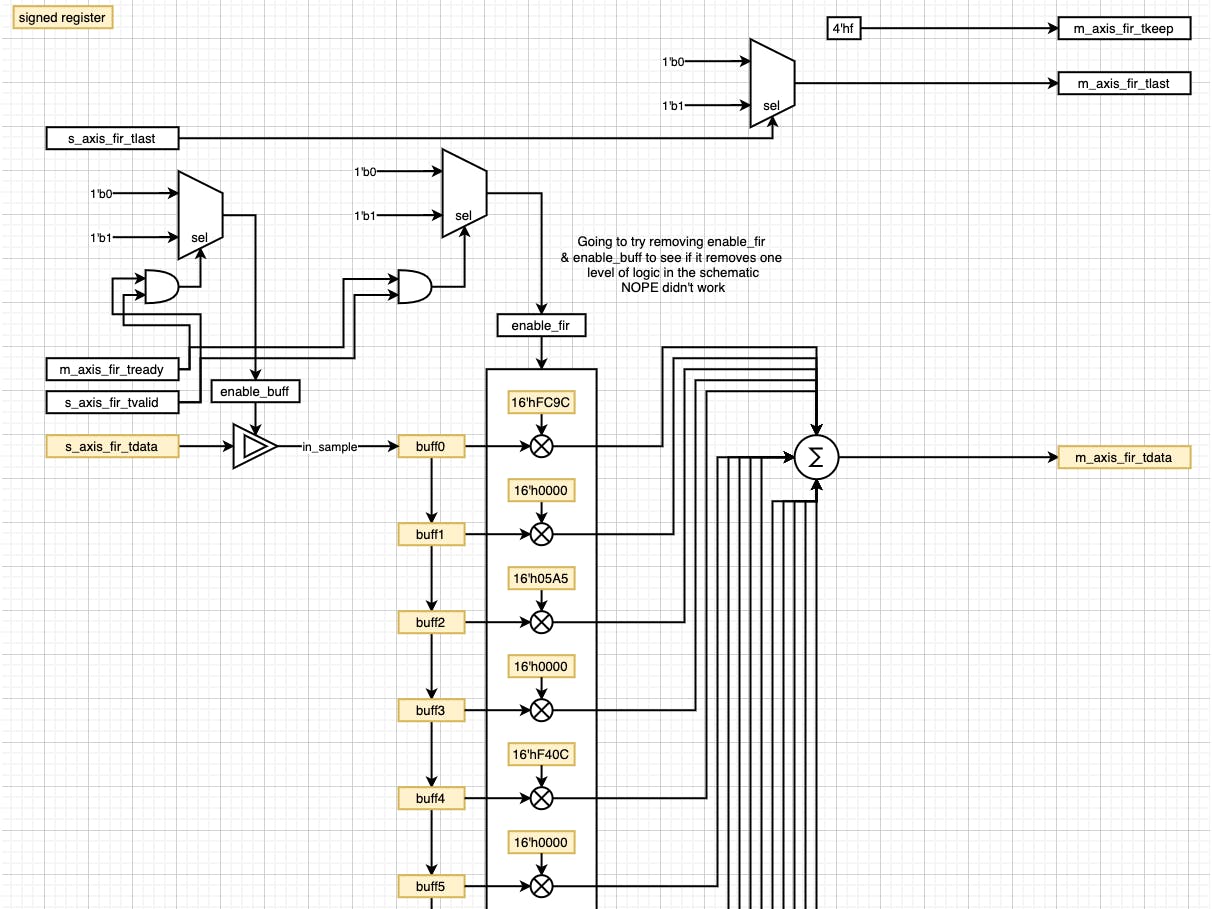

PDF) VHDL auto-generation tool for optimized hardware acceleration of convolutional neural networks on FPGA (VGT)

PDF) VHDL-based design and design methodology for reusable high performance direct digital requency synthesizers

Structured logic desing with VHDL-Skripta-Racunarski VLSI sistemi-Racunarska tehnika i informatika Part1 | Rezime' predlog Računarski sistemi | Docsity

Electronics | Free Full-Text | A Parallel Connected Component Labeling Architecture for Heterogeneous Systems-on-Chip

PDF) VHDL-based design and design methodology for reusable high performance direct digital requency synthesizers

Applied Sciences | Free Full-Text | Wind Power Short-Term Prediction Based on LSTM and Discrete Wavelet Transform

Amazon.com: OTM Essentials Pittsburg State University Tough Shell Phone Case, Classic : Everything Else

Amazon.com: OTM Essentials Pittsburg State University Tough Shell Phone Case, Classic : Everything Else

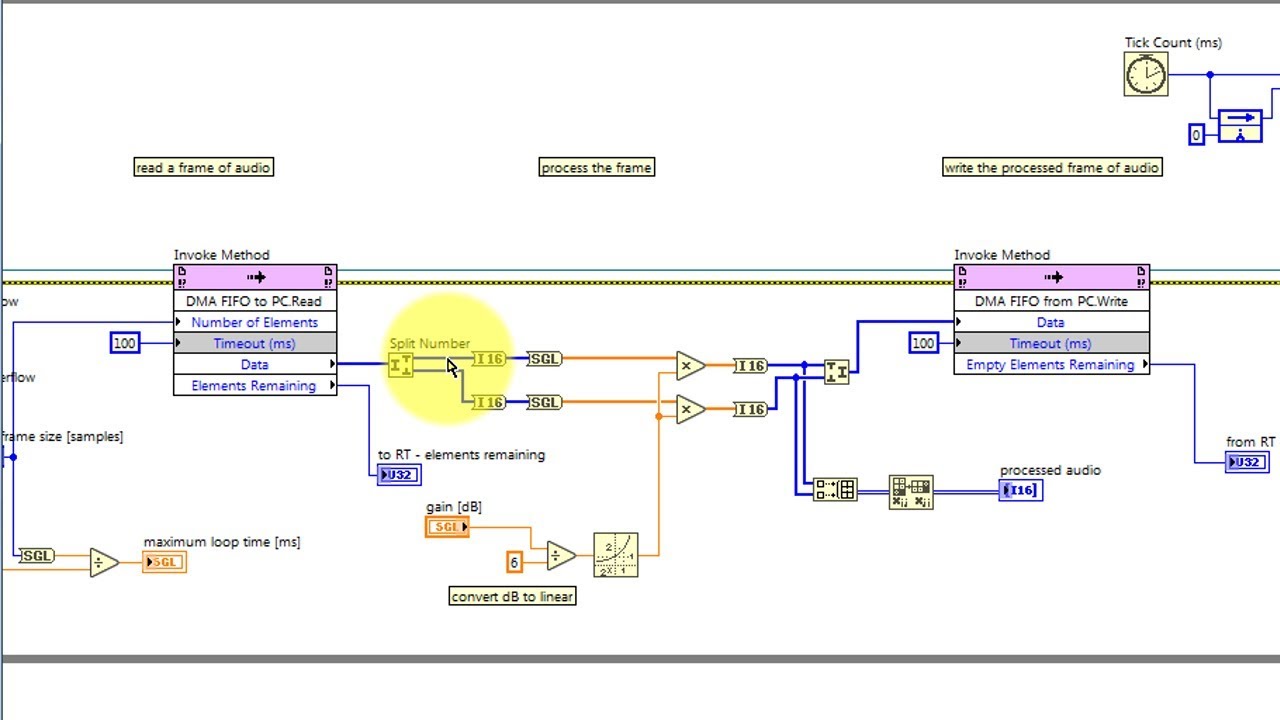

SDR TX Project Hardware / Software Update Jerry Boyd, WB8WFK (Hardware and FPGA VHDL ) Mike Pendley, K5ATM (PIC Software) October ppt download

2D FIR Filter IP Core User Guide Datasheet by Lattice Semiconductor Corporation | Digi-Key Electronics

![PDF] Hardware Pipeline for Rendering Clouds of Circular Points | Semantic Scholar PDF] Hardware Pipeline for Rendering Clouds of Circular Points | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/6d9742db7c7324595f9782146a2e49ae3da6c38e/4-Figure7-1.png)